## **General Description**

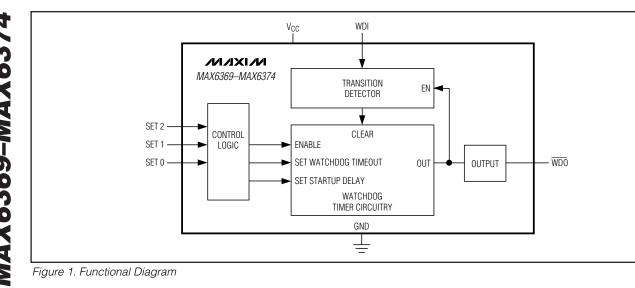

The MAX6369–MAX6374 are pin-selectable watchdog timers that supervise microprocessor ( $\mu$ P) activity and signal when a system is operating improperly. During normal operation, the microprocessor should repeatedly toggle the watchdog input (WDI) before the selected watchdog timeout period elapses to demonstrate that the system is processing code properly. If the  $\mu$ P does not provide a valid watchdog input transition before the timeout period expires, the supervisor asserts a watchdog (WDO) output to signal that the system is not executing the desired instructions within the expected time frame. The watchdog output pulse can be used to reset the  $\mu$ P or interrupt the system to warn of processing errors.

The MAX6369–MAX6374 are flexible watchdog timer supervisors that can increase system reliability through notification of code execution errors. The family offers several pin-selectable watchdog timing options to match a wide range of system timing applications:

- Watchdog startup delay: provides an initial delay before the watchdog timer is started.

- Watchdog timeout period: normal operating watchdog timeout period after the initial startup delay.

- Watchdog output/timing options: open drain (100ms) or push-pull (1ms).

The MAX6369–MAX6374 operate over a +2.5V to +5.5V supply range and are available in miniature 8-pin SOT23 packages.

#### Applications

Embedded Control Systems Industrial Controllers Critical µP and Microcontroller (µC) Monitoring Automotive Telecommunications Networking

#### **Features**

- Precision Watchdog Timer for Critical µP Applications

- Pin-Selectable Watchdog Timeout Periods

- Pin-Selectable Watchdog Startup Delay Periods

- Ability to Change Watchdog Timing Characteristics Without Power Cycling

- Open-Drain or Push-Pull Pulsed Active-Low Watchdog Output

- Watchdog Timer Disable Feature

- ♦ +2.5V to +5.5V Operating Voltage

- ♦ 8µA Low Supply Current

- No External Components Required

- Miniature 8-Pin SOT23 Package

#### **Ordering Information**

| DADT                | TEMP           | PIN-      | TOP   |

|---------------------|----------------|-----------|-------|

| PART                | RANGE          | PACKAGE   | MARKS |

| <b>MAX6369</b> KA-T | -40°C to +85°C | 8 SOT23-8 | AADC  |

| <b>MAX6370</b> KA-T | -40°C to +85°C | 8 SOT23-8 | AADD  |

| MAX6371KA-T         | -40°C to +85°C | 8 SOT23-8 | AADE  |

| <b>MAX6372</b> KA-T | -40°C to +85°C | 8 SOT23-8 | AADF  |

| <b>MAX6373</b> KA-T | -40°C to +85°C | 8 SOT23-8 | AADG  |

| MAX6374KA-T         | -40°C to +85°C | 8 SOT23-8 | AADH  |

| -                   |                |           |       |

*Note:* All devices are available in tape-and-reel only. Required order increment is 2,500 pieces.

#### Pin Configuration appears at end of data sheet.

#### \_Selector Guide

| PART    | OUTPUT     | WDO PULSE<br>WIDTH (ms) | MINIMUM STARTUP DELAY                  | MINIMUM WATCHDOG TIMEOUT |

|---------|------------|-------------------------|----------------------------------------|--------------------------|

| MAX6369 | Open Drain | 100                     | Selectable: 1ms to 60s                 | Selectable: 1ms to 60s   |

| MAX6370 | Push-Pull  | 1                       | Selectable: 1ms to 60s                 | Selectable: 1ms to 60s   |

| MAX6371 | Open Drain | 100                     | 60s                                    | Selectable: 1ms to 60s   |

| MAX6372 | Push-Pull  | 1                       | 60s                                    | Selectable: 1ms to 60s   |

| MAX6373 | Open Drain | 100                     | Selectable: 200µs to 60s or first edge | Selectable: 30µs to 10s  |

| MAX6374 | Push-Pull  | 1                       | Selectable: 200µs to 60s or first edge | Selectable: 30µs to 10s  |

## M/IXI/M

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

## ABSOLUTE MAXIMUM RATINGS

Terminal Voltage (with respect to GND)

| rennina venage (marreepeer te arre)     |                      |

|-----------------------------------------|----------------------|

| V <sub>CC</sub>                         | 0.3V to +6V          |

| WDI                                     | 0.3V to +6V          |

| WDO (Open Drain: MAX6369/71/73)         | 0.3V to +6V          |

| WDO (Push-Pull: MAX6370/72/740.3V       | to $(V_{CC} + 0.3V)$ |

| SET0, SET1, SET20.3V                    | to $(V_{CC} + 0.3V)$ |

| Maximum Current, Any Pin (input/output) | 20mA                 |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

|-------------------------------------------------------|----------------|

| SOT23-8 (derate 8.75mW/°C above +70°C)                | 700mW          |

| Operating Temperature Range                           | 40°C to +85°C  |

| Storage Temperature Range                             | 65°C to +150°C |

| Junction Temperature                                  |                |

| Lead Temperature (soldering, 10s)                     | +300°C         |

| V <sub>CC</sub> Rise or Fall Rate                     | 0.05V/µs       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(V<sub>CC</sub> = +2.5V to +5.5V, SET\_ = V<sub>CC</sub> or GND,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C and V<sub>CC</sub> = +3V.) (Note 1)

| PARAMETER                    | SYMBOL                   | CONDITIONS                                                                   |                                                           | MIN                   | ТҮР      | МАХ   | UNITS |  |

|------------------------------|--------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------------|----------|-------|-------|--|

| Operating Voltage Range      | Vcc                      |                                                                              |                                                           | 2.5                   |          | 5.5   | V     |  |

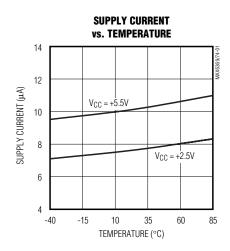

| Supply Current               | ICC                      | No load                                                                      |                                                           |                       | 8        | 20    | μA    |  |

| Input High Voltage           | VIH                      | WDI, SETO, SET1, SET                                                         | Γ2                                                        | $0.8 \times V_{CC}$   |          |       | V     |  |

|                              | Ma                       | WDI, SET0, SET1,                                                             | $V_{CC} \ge 3.3V$                                         |                       |          | 0.8   | 14    |  |

| Input Low Voltage            | VIL                      | SET2                                                                         | V <sub>CC</sub> ≥ 2.5V                                    |                       |          | 0.6   | V     |  |

| Logic Input Current (Note 2) |                          | WDI or SET_ = 0 or Vo                                                        | 00                                                        |                       | 0        | ±10   | nA    |  |

| WDO Output Low               |                          | I <sub>SINK</sub> = 1.2mA, V <sub>CC</sub> > output asserted                 | 2.7V, watchdog                                            |                       |          | 0.3   | V     |  |

| Voltage                      | V <sub>OL</sub>          | I <sub>SINK</sub> = 6mA, V <sub>CC</sub> > 4<br>output asserted              | $I_{SINK} = 6mA, V_{CC} > 4.5V, watchdog output asserted$ |                       |          | 0.4   | V     |  |

| WDO Leakage Current          | Ilkg                     | V <sub>NDO</sub> = 0 to +5.5V, output deasserted,<br>MAX6369/MAX6371/MAX6373 |                                                           |                       |          | 1     | μA    |  |

| WDO Output High              |                          | $I_{SOURCE} = 500\mu A, V_C$ output deasserted                               | <sub>C</sub> > 2.7V, watchdog                             | $0.8 \times V_{CC}$   |          |       | V     |  |

| Voltage                      | V <sub>OH</sub>          | $I_{SOURCE} = 800 \mu A$ , $V_{CC} > 4.5 V$ , watchdog output deasserted     |                                                           | V <sub>CC</sub> - 1.5 |          |       |       |  |

| MAX6369/MAX6370              |                          |                                                                              |                                                           |                       |          |       |       |  |

|                              |                          | SET2 = 0, SET1 = 0, S                                                        | SET0 = 0                                                  | 1                     |          | 3     |       |  |

|                              |                          | SET2 = 0, SET1 = 0, S                                                        | SET0 = $V_{CC}$                                           | 10                    |          | 30    | ms    |  |

|                              |                          | SET2 = 0, SET1 = $V_{CC}$                                                    | c, SET0 = 0                                               | 30                    |          | 90    |       |  |

| Startup Delay Period         |                          | SET2 = 0, SET1 = $V_{CC}$ , SET0 = $V_{CC}$                                  |                                                           | Watcho                | dog Disa | lbled |       |  |

|                              | <b><sup>t</sup>DELAY</b> | SET2 = $V_{CC}$ , SET1 = (                                                   | D, SETO = 0                                               | 100                   |          | 300   | ms    |  |

|                              |                          | SET2 = $V_{CC}$ , SET1 = (                                                   | D, SETO = $V_{CC}$                                        | 1                     |          | 3     |       |  |

|                              |                          | SET2 = $V_{CC}$ , SET1 = V                                                   | √ <sub>CC</sub> , SET0 = 0                                | 10                    | 30 s     |       | s     |  |

|                              |                          | SET2 = $V_{CC}$ , SET1 = V                                                   | V <sub>CC</sub> , SET0 = V <sub>CC</sub>                  | 60                    |          | 180   |       |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +2.5V \text{ to } +5.5V, \text{SET}_ = V_{CC} \text{ or GND}, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted}. Typical values are at T_A = +25^{\circ}\text{C} \text{ and } V_{CC} = +3V.)$  (Note 1)

| PARAMETER            | SYMBOL             | CONDITIONS                                                | MIN               | ТҮР                 | МАХ   | UNITS |  |

|----------------------|--------------------|-----------------------------------------------------------|-------------------|---------------------|-------|-------|--|

|                      |                    | SET2 = 0, SET1 = 0, SET0 = 0                              | 1                 |                     | 3     |       |  |

|                      |                    | SET2 = 0, SET1 = 0, SET0 = V <sub>CC</sub>                | 10                |                     | 30    | ms    |  |

|                      |                    | SET2 = 0, SET1 = $V_{CC}$ , SET0 = 0                      | 30                |                     | 90    | 1     |  |

| Watchdog Timeout     |                    | SET2 = 0, SET1 = V <sub>CC</sub> , SET0 = V <sub>CC</sub> | Watchdog Disabled |                     | abled |       |  |

| Period               | twD                | SET2 = V <sub>CC</sub> , SET1 = 0, SET0 = 0               | 100               |                     | 300   | ms    |  |

|                      |                    | SET2 = $V_{CC}$ , SET1 = 0, SET0 = $V_{CC}$               | 1                 |                     | 3     |       |  |

|                      |                    | SET2 = $V_{CC}$ , SET1 = $V_{CC}$ , SET0 = 0              | 10                |                     | 30    | s     |  |

|                      |                    | SET2 = $V_{CC}$ , SET1 = $V_{CC}$ , SET0 = $V_{CC}$       | 60                |                     | 180   |       |  |

| MAX6371/MAX6372      |                    |                                                           |                   |                     |       |       |  |

| Startup Dolay Pariod |                    | SET2 = 0, SET1 = $V_{CC}$ , SET0 = $V_{CC}$               | Watc              | hdog Disa           | abled |       |  |

| Startup Delay Period | <b>t</b> DELAY     | All other SET_ conditions                                 | 60                |                     | 180   | S     |  |

|                      |                    | SET2 = 0, SET1 = 0, SET0 = 0                              | 1                 |                     | 3     |       |  |

|                      |                    | SET2 = 0, SET1 = 0, SET0 = $V_{CC}$                       | 3                 |                     | 9     | ms    |  |

|                      |                    | SET2 = 0, SET1 = $V_{CC}$ , SET0 = 0                      | 10                |                     | 30    |       |  |

| Watchdog Time-Out    | 140                | SET2 = 0, SET1 = $V_{CC}$ , SET0 = $V_{CC}$               | Watchdog Disabled |                     |       |       |  |

| Period               | twd                | SET2 = $V_{CC}$ , SET1 = 0, SET0 = 0                      | 100               |                     | 300   |       |  |

|                      |                    | SET2 = $V_{CC}$ , SET1 = 0, SET0 = $V_{CC}$               | 300               |                     | 900   | ms    |  |

|                      |                    | SET2 = $V_{CC}$ , SET1 = $V_{CC}$ , SET0 = 0              | 3                 |                     | 9     | 0     |  |

|                      |                    | SET2 = $V_{CC}$ , SET1 = $V_{CC}$ , SET0 = $V_{CC}$       | 60                |                     | 180   | S     |  |

| MAX6373/MAX6374      |                    |                                                           |                   |                     |       |       |  |

|                      |                    | SET2 = 0, SET1 = 0, SET0 = 0                              | 3                 |                     | 9     | ms    |  |

|                      |                    | SET2 = 0, SET1 = 0, SET0 = $V_{CC}$                       | 3                 |                     | 9     | s     |  |

|                      |                    | SET2 = 0, SET1 = $V_{CC}$ , SET0 = 0                      | 60                |                     | 180   | 3     |  |

| Startup Delay Period |                    | SET2 = 0, SET1 = $V_{CC}$ , SET0 = $V_{CC}$               | Watchdog Disabled |                     | abled |       |  |

| Startup Delay I enou | <sup>t</sup> DELAY | SET2 = $V_{CC}$ , SET1 = 0, SET0 = 0                      | 200               |                     | 600   | μs    |  |

|                      |                    | SET2 = $V_{CC}$ , SET1 = 0, SET0 = $V_{CC}$               | First             | First Edge (Note 3) |       |       |  |

|                      |                    | SET2 = $V_{CC}$ , SET1 = $V_{CC}$ , SET0 = 0              | First             | Edge (No            | te 3) |       |  |

|                      |                    | SET2 = $V_{CC}$ , SET1 = $V_{CC}$ , SET0 = $V_{CC}$       | 60                |                     | 180   | S     |  |

|                      |                    | SET2 = 0, SET1 = 0, SET0 = 0                              | 3                 |                     | 9     | ms    |  |

|                      |                    | SET2 = 0, SET1 = 0, SET0 = $V_{CC}$                       | 3                 |                     | 9     | s     |  |

|                      | twd                | SET2 = 0, SET1 = $V_{CC}$ , SET0 = 0                      | 1                 |                     | 3     | 3     |  |

| Watchdog Timeout     |                    | SET2 = 0, SET1 = $V_{CC}$ , SET0 = $V_{CC}$               | Watchdog Disabled |                     | abled |       |  |

| Period               |                    | SET2 = $V_{CC}$ , SET1 = 0, SET0 = 0                      | 30                |                     | 90    | μs    |  |

|                      |                    | SET2 = $V_{CC}$ , SET1 = 0, SET0 = $V_{CC}$               | 1                 |                     | 3     |       |  |

|                      |                    | SET2 = $V_{CC}$ , SET1 = $V_{CC}$ , SET0 = 0              | 10                |                     | 30    | s     |  |

|                      |                    | SET2 = $V_{CC}$ , SET1 = $V_{CC}$ , SET0 = $V_{CC}$       | 10                |                     | 30    |       |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

(V<sub>CC</sub> = +2.5V to +5.5V, SET\_ = V<sub>CC</sub> or GND,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C and V<sub>CC</sub> = +3V.) (Note 1)

| PARAMETER                              | SYMBOL         | CONDITIONS              | MIN | ТҮР | МАХ | UNITS |

|----------------------------------------|----------------|-------------------------|-----|-----|-----|-------|

| Watchdog Input Pulse Width<br>(Note 2) | twdi           | After WDO deasserted    | 100 |     |     | ns    |

| Watabdag Output Dulas Width            | 1.17.0         | MAX6369/MAX6371/MAX6373 | 100 |     | 300 | ms    |

| Watchdog Output Pulse Width            | twdo           | MAX6370/MAX6372/MAX6374 | 1   |     | 3   | ms    |

| Internal Setup Time<br>(Note 4)        | <b>t</b> SETUP | After WDO deasserted    | 100 |     | 300 | μs    |

Note 1: Production tested at  $T_A = +25^{\circ}C$ . Guaranteed by design over temperature limits.

Note 2: Guaranteed by design.

Note 3: In this setting the watchdog timer is inactive and startup delay ends when WDI sees its first level transition. See *Selecting Device Timing* for more information.

Note 4: After power-up, or a setting change, there is an internal setup time during which WDI is ignored.

| (Circuit of Figure 1 | $T_A = +25^{\circ}C$ , unless | otherwise noted ) |

|----------------------|-------------------------------|-------------------|

| (On our of Figure 1) | $T_{A} = 120.0$ , unicou      |                   |

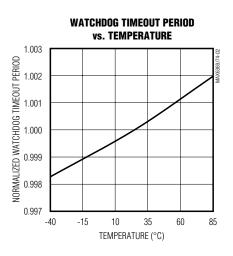

## **Typical Operating Characteristics**

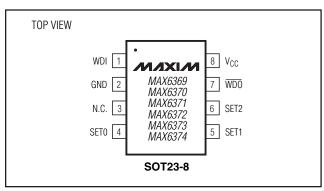

#### **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                     |

|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | WDI             | Watchdog Input. If WDI remains either high or low for the duration of the watchdog timeout period ( $t_{WD}$ ), $\overline{WDO}$ triggers a pulse. The internal watchdog timer clears whenever a $\overline{WDO}$ is asserted or whenever WDI sees a rising or falling edge. |

| 2   | GND             | Ground                                                                                                                                                                                                                                                                       |

| 3   | N.C.            | Not Connected. Do not make any connection to this pin.                                                                                                                                                                                                                       |

| 4   | SET0            | Set Zero. Logic input for selecting startup delay and watchdog timeout periods. See Table 1 for timing details.                                                                                                                                                              |

| 5   | SET1            | Set One. Logic input for selecting startup delay and watchdog timeout periods. See Table 1 for timing details.                                                                                                                                                               |

| 6   | SET2            | Set Two. Logic input for selecting startup delay and watchdog timeout periods. See Table 1 for timing details.                                                                                                                                                               |

| 7   | WDO             | Watchdog Output. Pulses low for the watchdog output pulse width, t <sub>WDO</sub> , when the internal watchdog times out. The MAX6369/MAX6371/MAX6373 have open-drain outputs and require a pull-up resistor. The MAX6370/MAX6372/MAX6374 outputs are push-pull.             |

| 8   | V <sub>CC</sub> | Supply Voltage (+2.5V to +5.5V)                                                                                                                                                                                                                                              |

#### **Table 1. Minimum Timeout Settings**

| LC   | OGIC INPUTS |      | MAX6369/MAX6370 | MAX6371/MAX6372                      | MAX6373    | /MAX6374 |

|------|-------------|------|-----------------|--------------------------------------|------------|----------|

| SET2 | SET1        | SET0 | tDELAY, tWD     | tDELAY, tWD tDELAY = 60s, tWD tDELAY |            | twp      |

| 0    | 0           | 0    | 1ms             | 1ms                                  | 3ms        | 3ms      |

| 0    | 0           | 1    | 10ms            | 3ms                                  | 3s         | Зs       |

| 0    | 1           | 0    | 30ms            | 10ms                                 | 60s        | 1s       |

| 0    | 1           | 1    | Disabled        | Disabled                             | Disabled   | Disabled |

| 1    | 0           | 0    | 100ms           | 100ms                                | 200µs      | 30µs     |

| 1    | 0           | 1    | 1s              | 300ms                                | First Edge | 1s       |

| 1    | 1           | 0    | 10s             | 3s                                   | First Edge | 10s      |

| 1    | 1           | 1    | 60s             | 60s                                  | 60s        | 10s      |

## **Detailed Description**

The MAX6369–MAX6374 are flexible watchdog circuits for monitoring  $\mu$ P activity. During normal operation, the internal timer is cleared each time the  $\mu$ P toggles the WDI with a valid logic transition (low to high or high to low) within the selected timeout period (twD). The WDO remains high as long as the input is strobed within the selected timeout period. If the input is not strobed before the timeout period expires, the watchdog output is asserted low for the watchdog output pulse width (twDO). The device type and the state of the three logic control pins (SET0, SET1, and SET2) determine watchdog timing characteristics. The three basic timing variations for the watchdog startup delay and the normal watchdog timeout period are summarized below (see Table 1 for the timeout characteristics for all devices in the family):

• Watchdog Startup Delay:

Provides an initial delay before the watchdog timer is started.

Allows time for the  $\mu$ P system to power up and initialize before assuming responsibility for normal watchdog timer updates.

Includes several fixed or pin-selectable startup delay options from 200µs to 60s, and an option to wait for the first watchdog input transition before starting the watchdog timer.

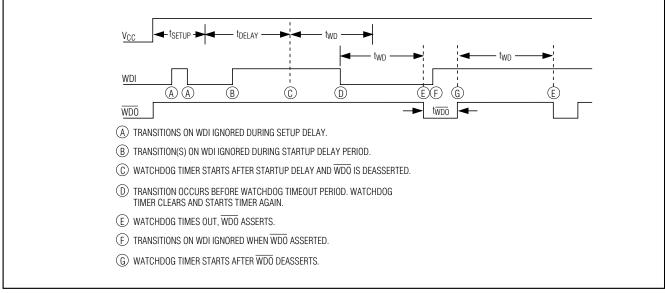

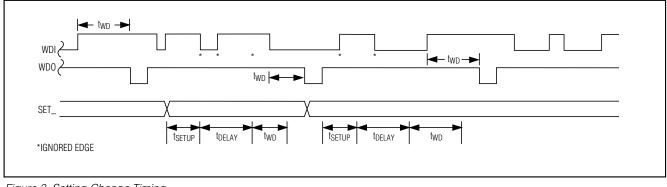

Figure 2. Watchdog Timing

• Watchdog Timeout Period:

Normal operating watchdog timeout period after the initial startup delay.

A watchdog output pulse is asserted if a valid watchdog input transition is not received before the timeout period elapses.

Eight pin-selectable timeout period options for each device, from 30µs to 60s.

Pin-selectable watchdog timer disable feature.

• Watchdog Output/Timing Options:

Open drain, active low with 100ms minimum watchdog output pulse (MAX6369/MAX6371/MAX6373).

Push-pull, active low with 1ms minimum watchdog output pulse (MAX6370/MAX6372/MAX6374).

Each device has a watchdog startup delay that is initiated when the supervisor is first powered or after the user modifies any of the logic control set inputs. The watchdog timer does not begin to count down until the

completion of the startup delay period, and no watchdog output pulses are asserted during the startup delay. When the startup delay expires, the watchdog begins counting its normal watchdog timeout period and waiting for WDI transitions. The startup delay allows time for the  $\mu$ P system to power up and fully initialize before assuming responsibility for the normal watchdog timer updates. Startup delay periods vary between the different devices and may be altered by the logic control set pins. To ensure that the system generates no undesired watchdog outputs, the routine watchdog input transitions should begin before the selected minimum startup delay period has expired.

The normal watchdog timeout period countdown is initiated when the startup delay is complete. If a valid logic transition is not recognized at WDI before the watchdog timeout period has expired, the supervisor asserts a watchdog output. Watchdog timeout periods vary between the different devices and may be altered by the logic control set pins. To ensure that the system generates no undesired watchdog outputs, the watchdog input transitions should occur before the selected minimum watchdog timeout period has expired.

The startup delay and the watchdog timeout period are determined by the states of the SET0, SET1, and SET2 pins, and by the particular device within the family. For the MAX6369 and MAX6370, the startup delay is equal to the watchdog timeout period. The startup and watchdog timeout periods are pin selectable from 1ms to 60s (minimum).

For the MAX6371 and MAX6372, the startup delay is fixed at 60s and the watchdog timeout period is pin selectable from 1ms to 60s (minimum).

The MAX6373/MAX6374 provide two timing variations for the startup delay and normal watchdog timeout. Five of the pin-selectable modes provide startup delays from 200µs to 60s minimum, and watchdog timeout

delays from 3ms to 10s minimum. Two of the selectable modes do not initiate the watchdog timer until the device receives its first valid watchdog input transition (there is no fixed period by which the first input must be received). These two extended startup delay modes are useful for applications requiring more than 60s for system initialization.

All the MAX6369–MAX6374 devices may be disabled with the proper logic control pin setting (Table 1).

#### **Applications Information**

#### **Input Signal Considerations**

Watchdog timing is measured from the last WDI rising or falling edge associated with a pulse of at least 100ns in width. WDI transitions are ignored when  $\overline{WDO}$  is asserted, and during the startup delay period (Figure 2). Watchdog input transitions are also ignored for a setup period, t<sub>SETUP</sub>, of up to 300µs after power-up or a setting change (Figure 3).

#### **Selecting Device Timing**

SET2, SET1, and SET0 program the startup delay and watchdog timeout periods (Table 1). Timeout settings can be hard wired, or they can be controlled with logic gates and modified during operation. To ensure smooth transitions, the system should strobe WDI immediately before the timing settings are changed. This minimizes the risk of initializing a setting change too late in the timer countdown period and generating undesired watchdog outputs. After changing the timing settings, two outcomes are possible based on  $\overline{WDO}$ . If the change is made while WDO is asserted, the previous setting is allowed to finish, the characteristics of the new setting are assumed, and the new startup phase is entered after a 300µs setup time (tSETUP) elapses. If the change is made while  $\overline{\text{WDO}}$  is not asserted, the new setting is initiated immediately, and the new startup phase is entered after the 300µs setup time elapses.

Figure 3. Setting Change Timing

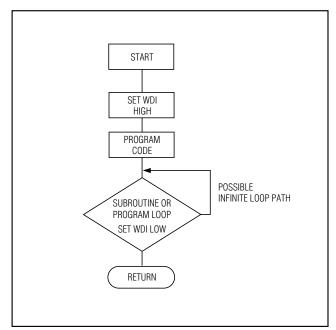

Figure 4. Watchdog Flow Diagram

Selecting 011 (SET2 = 0, SET1 = 1, SET0 = 1) disables the watchdog timer function on all devices in the family. Operation can be reenabled without powering down by changing the set inputs to the new desired setting. The device assumes the new selected timing characteristics and enter the startup phase after the  $300\mu$ s setup time elapses (Figure 3).

The MAX6373/MAX6374 offer a first-edge feature. In first-edge mode (settings 101 or 110, Table 1), the internal timer does not control the startup delay period. Instead, startup terminates when WDI sees a transition. If changing to first-edge mode while the device is operating, disable mode must be entered first. It is then safe to select first-edge mode. Entering disable mode first ensures the output is unasserted when selecting first-edge mode and removes the danger of WDI being masked out.

#### Output

The MAX6369/MAX6371/MAX6373 have an active-low, open-drain output that provides a watchdog output pulse of 100ms. This output structure sinks current when WDO is asserted. Connect a pullup resistor from WDO to any supply voltage up to +5.5V.

Select a resistor value large enough to register a logic low (see *Electrical Characteristics*), and small enough to register a logic high while supplying all input current and leakage paths connected to the WDO line. A 10k $\Omega$ pullup is sufficient in most applications. The MAX6370/ MAX6372/MAX6374 have push-pull outputs that provide an active-low watchdog output pulse of 1ms. When WDO deasserts, timing begins again at the beginning of the watchdog timeout period (Figure 2).

#### **Usage in Noisy Environments**

If using the watchdog timer in an electrically noisy environment, a bypass capacitor of  $0.1\mu$ F should be connected between V<sub>CC</sub> and GND as close to the device as possible, and no further away than 0.2 inches.

#### \_Watchdog Software Considerations

To help the watchdog timer monitor software execution more closely, set and reset the watchdog input at different points in the program, rather than pulsing the watchdog input high-low-high or low-high-low. This technique avoids a stuck loop, in which the watchdog timer would continue to be reset inside the loop, keeping the watchdog from timing out. Figure 4 shows an example of a flow diagram where the I/O driving the watchdog input is set high at the beginning of the program, set low at the end of every subroutine or loop, then set high again when the program returns to the beginning. If the program should hang in any subroutine, the problem would be quickly corrected, since the I/O is continually set low and the watchdog timer is allowed to time out, causing WDO to pulse.

## **Pin Configuration**

#### Chip Information

TRANSISTOR COUNT: 1500 PROCESS: BICMOS

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

- 8

- © 2003 Maxim Integrated Products

- Printed USA

**MAXIM** is a registered trademark of Maxim Integrated Products.

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.